串行进位加法器设计/Ripple-Carry Adder

串行/行波进位 & 串行/行波进位加法器

回顾一位 FA (全加器)的设计,不难看到 FA 同时考虑了前一位的进位和本位计算结果产生的进位。

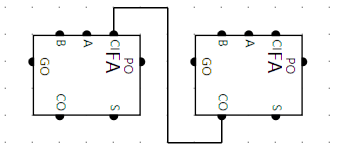

容易联想到将前一位产生的进位输出到下一个 FA 的,串行地联系每位间的进位关系,电路如所示

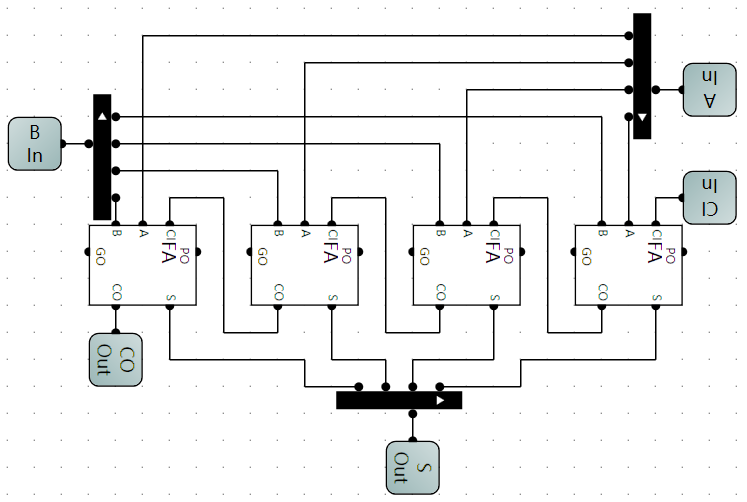

第位 FA 的通过从第个 FA 的获得进位的方式,叫做串行/行波进位,像这样得到加法器叫串行进位加法器,或者叫行波进位加法器(RCA)。串行连接4个 FA 可以组成一个4位加法器,可以进行两个4位二进制数的加法运算。电路如所示

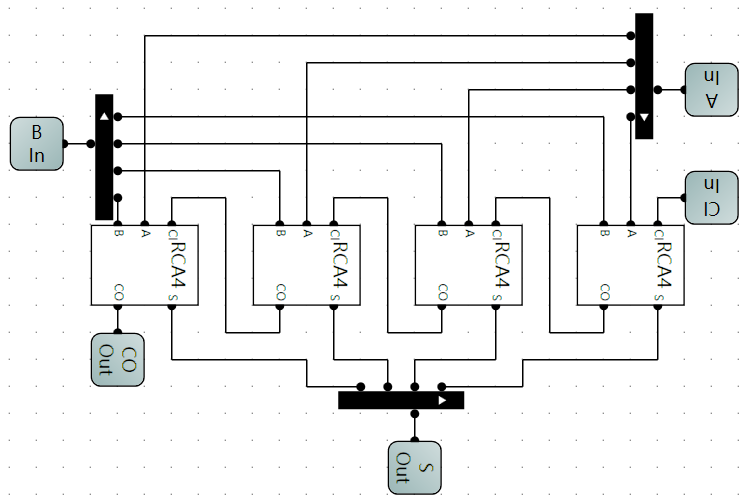

如法炮制,将一个4位 RCA 视为一组,将4组4位 RCA 用串行进位的方式连接起来就得到了一个组内串行进位且组间串行进位的16位串行进位加法器。电路如所示

分析串行进位加法器的不足

由于串行连接的方式,使得每位 FA 做位加法运算时,需要等待前一位 FA 得出进位位的结果才能进行本位的逻辑运算。这使得越高位的 FA 等待进位参与本位运算的时间越长,降低了运算效率。